博通公司(Broadcom)近日宣布推出其最新的3.5D eXtreme Dimension系统级封装(XDSiP)平台技术,可以支持大规模人工智能(AI)和高性能计算(HPC)工作负载。该平台专为消费级AI客户设计,助力他们开发下一代定制加速器(XPU)。3.5D XDSiP在单一封装设备中集成了超过6000平方毫米的硅片和多达12个高带宽内存(HBM)堆栈,实现了大规模AI的高效、低功耗计算。

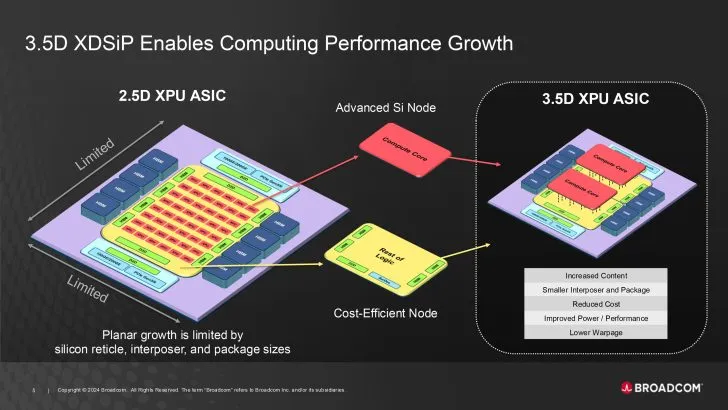

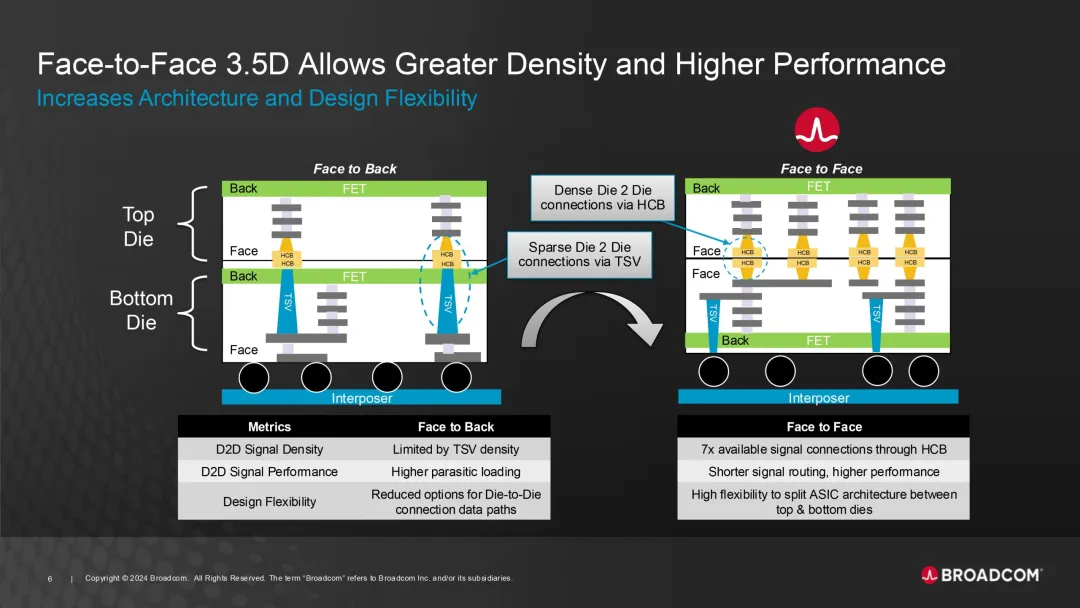

这是业界首款Face-to-Face(F2F)3.5D XPU,可以说是封装技术领域的一个重要里程碑。与传统的2.5D集成相比,3.5D XDSiP结合了3D硅片堆叠和2.5D封装,能够更好地满足新一代大型语言模型(LLM)的复杂计算需求,优化尺寸、功耗和成本。3.5D集成被视为未来十年下一代XPU的首选技术。

3.5D XDSiP平台在互连密度和功率效率上取得了较大提升。与F2B技术相比,堆叠芯片之间的信号密度提高了七倍,功耗降低了十倍。此外,该平台最大限度地减少了3D堆栈内计算、内存和I/O组件之间的延迟,实现了更紧凑的封装尺寸,降低了成本并改善了封装翘曲问题。

博通的3.5D XDSiP集成了四个计算芯片、一个I/O芯片和六个HBM模块,充分利用了台积电的尖端5nm工艺节点和2.5D CoWoS封装技术。公司专有的设计流程和自动化方法基于行业标准工具,确保了即使在芯片复杂度极高的情况下,也能实现一次通过的成功设计。3.5D XDSiP平台已展示出关键IP模块的完整功能和卓越性能,包括高速SerDes、HBM内存接口和芯片间互连,说明博通在复杂3.5D集成电路设计和测试方面的具备一定的专业能力。

博通与台积电在过去几年中紧密合作,将台积电最先进的逻辑工艺和3D芯片堆叠技术与博通的设计专长相结合。台积电业务发展与全球销售高级副总裁兼副联席首席运营官Kevin Zhang博士表示:“我们期待将该平台产品化,以释放人工智能创新并促进未来发展。”

此外,博通还透露,字节跳动作为TikTok母公司,正在与博通合作,利用台积电5nm工艺开发AI芯片。

目前,博通已有五种以上的3.5D产品在开发中,大多数消费级AI客户已采用了3.5D XDSiP平台技术,预计将于2026年2月开始生产出货。博通表示,3.5D XDSiP平台的推出将大幅推动AI和HPC领域的发展,满足日益增长的计算需求。