随着科学研究和工业生产对数据处理能力的需求不断攀升,高性能计算(HPC)已成为推动这些领域进步的重要力量。在这样的背景下,计算机技术尤其是互连技术的进步显得尤为关键。Compute Express Link(CXL)作为新一代的高速互连技术,因其在带宽、延迟和扩展性方面的优势,正展现出在HPC领域的广泛应用潜力,有可能彻底改变数据中心和加速器之间的通信方式,从而推动HPC领域的革命性进步。

然而,为了充分发挥CXL的价值,软件必须得及时跟得上技术的发展,所以,其中的关键是开发针对SoC(System on Chip)设计师所需的硬件生态系统的软件框架。这意味着我们需要构建支持CXL的全面软件解决方案,以简化应用开发,确保硬件的充分利用,并最终实现系统级的优化。

三种CXL设备解锁HPC全新潜能 #

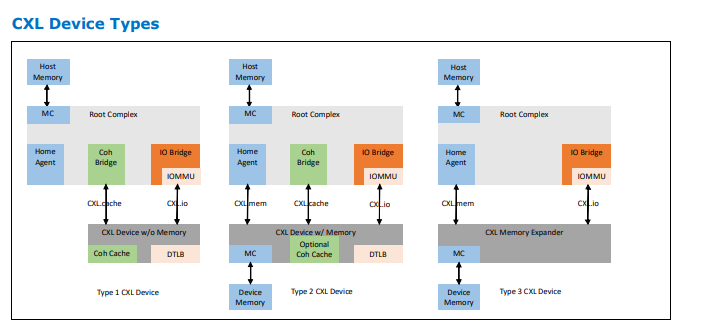

CXL主要由三种协议构成:CXL.io、CXL.cache 和 CXL.mem。具体来说,CXL.io被视为是PCIe通信的低延迟备选,它们在很多场合上可以互相替代。CXL.io为I/O设备带来了增强且非一致的加载/存储接口。CXL.cache为相关设备提供了在系统内存中建立一致性缓存的能力,并通过请求与响应方式为低延迟I/O事务创建缓存。而CXL.mem则与CXL.cache的功能相反,它允许主机处理器直接访问通过CXL连接的设备,尤其是那些具备低延迟加载/存储指令集的存储设备。

这三种协议能够以不同方式组合,支持三种不同类型的设备,为方便起见,分别简称为类型1、类型2和类型3。

-

类型1设备融合了CXL.io和CXL.cache协议,允许无内部存储器的智能 NIC 或加速器等设备直接控制和访问系统存储器的区域。

-

类型2设备在类型1的基础上,拥有额外的或内置的存储,并利用所有协议来允许系统或设备以两者间硬件支持的一致性在另一个存储器中分配区域。这两个不同的方向(由系统启动或由主机启动)分别称为主机偏置或设备偏置模式。

-

类型3设备是由CXL.io和CXL.mem协议支持的存储设备,它们能够在DRAM、NVRAM和其他各类持久性及易失性存储设备上实现字节级内存寻址。通过这种架构,主机能够像访问本地内存一样访问其他系统的额外内存和专用内存扩展器。

下图显示了这三种设备类型。

图 1:CXL设备类型,摘自 Compute Express Link Specification r.3.0,v1.0

相较于传统的PCIe事务,CXL.mem和CXL.cache拥有更低的延迟。例如,PCIe 5.0常见的延迟大约是100纳秒,而CXL 2.0只有20-40纳秒。CXL.mem所带来的延迟降低,使得通过利用类型3设备可以进行内存扩展。这意味着应用程序线程可以访问系统外的存储器,同时避免了因内存不足而导致作业失败的风险,这一功能被称为“内存池”。通过CXL 2.0得到加强,并可通过支持交换机附加内存来拓展此范式。这不仅让系统能外加内存,还可以向其他系统提供未使用的本地内存,从而提高利用率和降低初始系统成本。

CXL 3.0 规范中引入的内存共享允许多个主机访问给定的 CXL 附加内存分配。它还定义了结构连接内存扩展器的概念——这些设备可以包含各种类型的内存,以便进行池化和共享,并且可以实现本地内存分层,以代表主机优化池的性能特性。这为Cray Research定义的 SHMEM协议创造了一个有趣的替代方案,使多个主机对共享内存池进行极低延迟访问。由于本机总线互连介质,这不仅提供了比 SHMEM 库例程更好的性能,而且还为该共享内存池上的并行计算提供了可能简单得多的编程模型。

CXL延迟降低的另一个内在价值是,它还具有促进设备到设备内存事务的潜力,例如在一个或多个系统中使用多个 GPU,不需要花费专有的辅助总线或软件层来互连这些设备。这一点在小型AI训练场景中尤为明显,因为可以轻松展示即时性能影响。这种通过结构性连接将远程硬件直接整合进共享内存系统的方法,可能会开启AI训练的新篇章,特别是在数据中心,因为 CXL 引入了对称的对等设备通信功能,从而减少了对CPU的持续依赖。

总的来说,CXL结构为服务器分解提供了机会,有助于克服由于资源不在本地系统架构中而限制特定应用程序工作流的问题。例如,当存储可以被集中到通过结构连接的扩展器中,每个系统对独立(且孤立)存储的需求就会减少。专用内存总线和CXL提供的附加带宽有助于解决核心内存带宽瓶颈,允许设计和配置单个服务器,更注重性能而不是容量。要实现这一愿景,关键在于开发具有低延迟的CXL交换功能和灵活的内存分层系统,这些功能需要在支持软件和扩展器硬件中实现。

新思科技新方案,保障CXL的完整性和数据加密 #

鉴于 CXL 2.0中的外部交换和 CXL 3.0 中的增强结构的引入,随着数据在服务器外部电缆上传输,增强的总线安全性变得至关重要。因此,为了保护数据免受未经授权的访问或篡改,PCIe和CXL控制器可以使用完整性和数据加密 (IDE) 安全IP模块,即使是在数据被外部人员接触的情况下,也能确保数据的安全和隐私。

面对日益增长的安全需求,新思科技推出了一种创新方案,将高安全性的CXL控制器与符合标准的、可定制的IDE安全模块相结合。这一技术的目的是确保数据在SoC内部的传输过程中免遭篡改和物理攻击的威胁。更具体地说,该方案可以在 CXL.cache/.mem 协议情况下为 FLIT 提供保密性、完整性和重放保护,并在 CXL.io 的情况下为事务层数据包 (TLP) 提供保密性、完整性和重放保护。值得一提的是,这个系统不仅与控制器的数据接口总线宽度和通道配置相匹配,且在面积、性能和延迟方面都经过了精心优化,甚至在CXL.cache/.mem滑动模式情况下,可以实现几乎零延迟的数据传输。

CXL的未来展望 #

在经历了多年对OpenCAPI、GenZ等一致性协议的标准化努力后,整个行业开始聚焦于CXL。CXL控制器将采用一种名为“信用可扩展流”(CXS)的流接口协议,这种协议通过封装更新的CCIX版本,为多处理器架构带来了对称一致性。这一做法最初因为一致性成本的上升而在原生形态下遭遇了较高的延迟,尤其是在处理小型写入操作时。CXS.B(CXS的CXL托管版本)通过提供专门用于CPU间对称通信的流媒体通道对,巧妙地解决了这一挑战。

CXL技术的发展和应用正在深刻改变高性能计算领域,对于降低延迟、实现内存资源共享和服务器的功能解耦,都展现出了明显的进步和潜力。随着软件框架的不断完善,这种技术有望开启计算性能和效率的新纪元,满足日益增长的硬件生态系统的需求。作为PCIe和CXL物理层、控制器以及IDE和验证IP的领先提供商,新思科技凭借在超过1800个设计项目中的集成和验证经验,可以显著降低风险,协助SoC工程师加快产品推向市场的进程。