Intel Nova Lake Leak: Core Wars Enter a New Era

Intel’s next-generation Nova Lake (NVL) architecture is shaping up to be a decisive escalation in the ongoing CPU arms race. While AMD pushes efficiency and cache innovation with Zen 6, Intel appears ready to deploy a core-density “nuclear option”—leveraging a dual-die design and massive thread counts to reclaim performance leadership.

⚙️ Architecture: Dual-Compute Die Strategy #

At the heart of Nova Lake is a shift to a Dual-Compute Tile design. Instead of a single monolithic die, Intel splits compute resources across two tiles, dramatically increasing scalability.

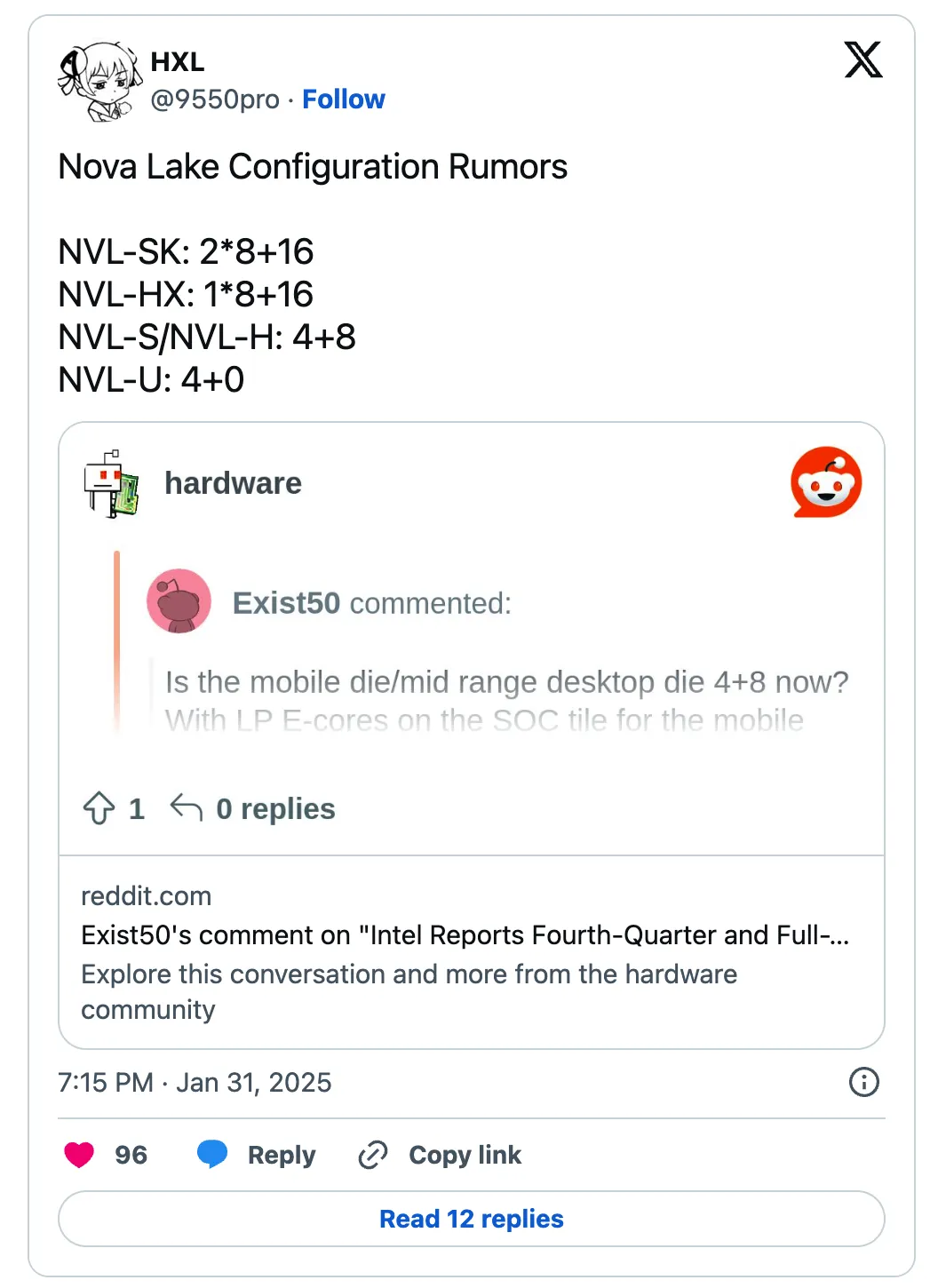

| Variant | Rumored Configuration | Target Segment |

|---|---|---|

| Nova Lake-S (Flagship) | 16 P-Cores + 32 E-Cores (64 Threads) | Enthusiast / High-End Desktop |

| Nova Lake-HX | 8 P-Cores + 16 E-Cores | Mobile Workstations |

| Nova Lake-U | 4 P-Cores (No E-Cores) | Ultra-Thin Laptops |

This approach allows Intel to push core counts far beyond traditional limits—but introduces new latency and scheduling complexities.

🚀 PCIe 6.0: Bandwidth Explosion #

Nova Lake is expected to debut PCIe 6.0, doubling down on next-gen I/O performance:

- Speed: 128 GT/s (per lane)

- Benefit: Massive throughput for AI accelerators and NVMe storage

- Challenge: Requires ultra-high PCB quality and tighter signal integrity control

This isn’t just an upgrade—it’s a platform-level shift that will impact motherboard design, power delivery, and thermal layouts.

⚠️ The Latency Trade-Off #

Splitting compute across two dies introduces a key risk:

- ~23% higher inter-die latency (rumored)

- Potential bottlenecks in:

- High-FPS gaming

- Latency-sensitive workloads

- Minimal impact on:

- Rendering

- Highly parallel compute tasks

This creates a familiar trade-off: throughput vs. responsiveness.

🏭 Manufacturing Crossroads: 18A vs TSMC #

Intel faces a critical decision on how to manufacture Nova Lake:

Option 1: TSMC N3B #

- Proven yields

- High cost

- External dependency

Option 2: Intel 18A #

- RibbonFET (GAA transistors)

- PowerVia (backside power delivery)

- Current yield concerns (~58%)

The success of Nova Lake may hinge less on architecture—and more on whether Intel can execute 18A at scale.

⚔️ Nova Lake vs Zen 6: Philosophy Clash #

The 2026 CPU battle is shaping into two distinct strategies:

Intel (Nova Lake) #

- Approach: Brute-force scaling

- Goal: Maximum multi-threaded performance

- Metric: +40% class gains in rendering benchmarks

AMD (Zen 6) #

- Approach: Efficiency + cache optimization

- Goal: Better performance-per-watt

- Advantage: 3D V-Cache for latency-sensitive workloads

Key Insight: More cores don’t guarantee better performance—communication efficiency increasingly defines real-world results.

🧠 The Software Bottleneck: Thread Scheduling #

Hardware alone won’t determine success. Nova Lake depends heavily on:

- Windows Thread Director improvements

- Better utilization of E-cores

- Reduced scheduling overhead

Current hybrid CPUs still struggle:

- E-core utilization in complex workloads can drop below 80%

- Inefficient scheduling wastes theoretical performance

Without software alignment, Nova Lake risks becoming a spec-sheet champion with real-world inefficiencies.

🧩 Final Verdict: Power vs. Precision #

Nova Lake represents Intel’s most aggressive attempt yet to reclaim leadership through sheer computational scale. But in modern computing, success depends on more than raw numbers.

- Intel is betting on core count and bandwidth

- AMD is betting on efficiency and latency

The winner of the next generation won’t be the chip with the most cores—it will be the one where cores communicate fastest and smartest.